Problem Addressed

Programming FPGAs for hardware acceleration is a complex and time-consuming task that requires specific skills and tools that are different from typical software development.

In addition, current HLS tools allow software developers to use C-like languages to program FPGA, still require hardware expertise and manual code transformations and directives to generate efficient hardware implementations. This affects productivity, performance, and energy efficiency of FPGA-based systems, especially for applications that involve data-intensive and parallel computations, such as image processing, machine learning, and DSP algorithms.

Technology

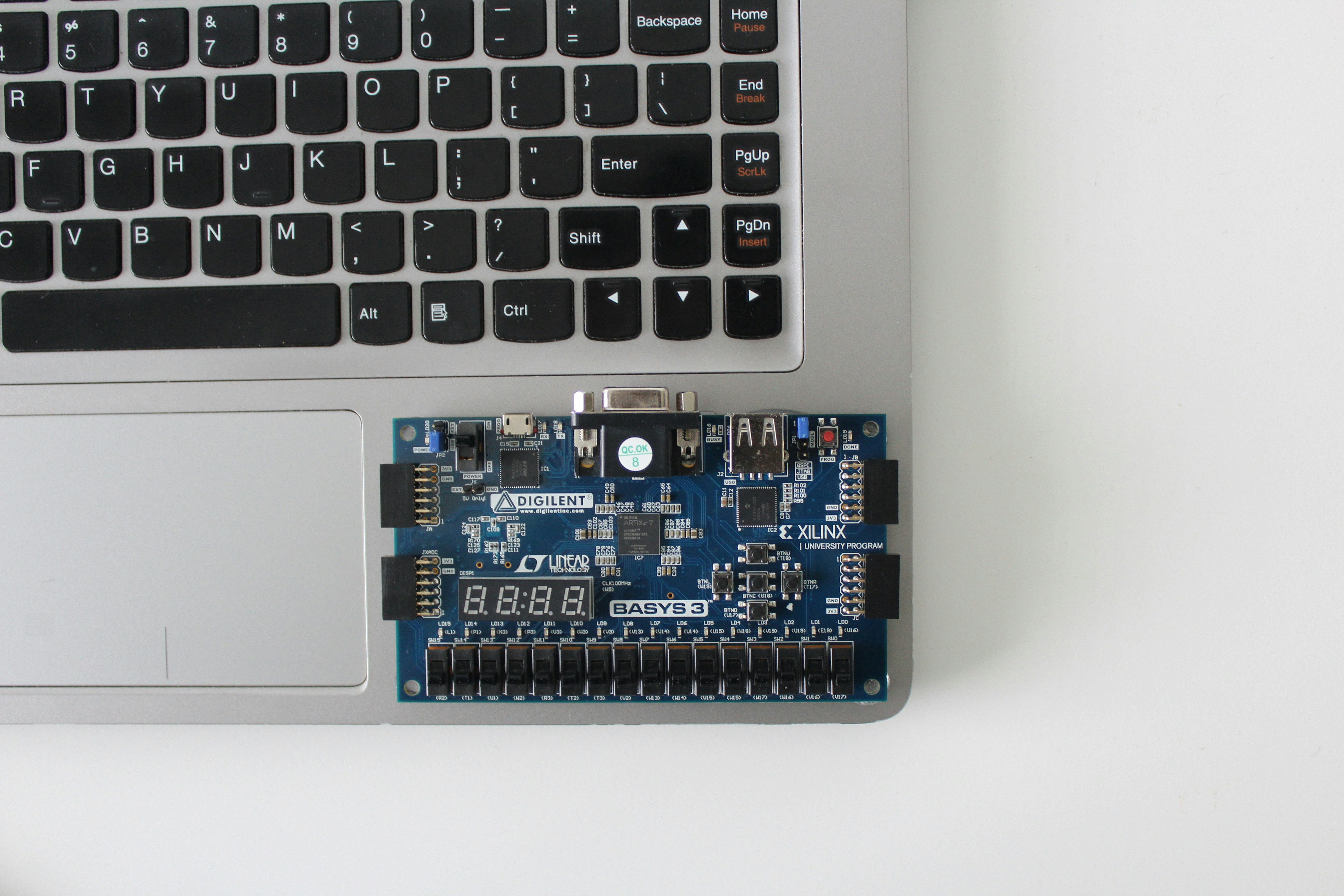

Our solution is CHARD, a software that automatically restructures code, transforming C code into a dataflow graph (DFG) and applies graph optimizations to generate C code with high-level synthesis (HLS) directives for FPGA-based hardware accelerators. The technology aims to enable software developers to program FPGAs more easily and efficiently, without requiring deep knowledge of hardware design or HLS tools.

The technology is based on a flexible frontend that can handle different input languages and a backend that implements various graph transformations and optimizations, such as folding, unfolding, pipelining, arithmetic optimizations, array partitioning, and data reuse. CHARD is implemented in a framework that can automatically generate HLS-friendly C code from execution traces of the input critical functions, achieving speedups of 30-100 times (vs original unmodified C code) and 2-15 faster (vs C optimized with Vivado HLS directives).

Advantages

Versatility - Supports different input programming language;

User-friendly - Simpler instructions than HLS tools eliminating the need for deep HLS knowledge;

Performance - Automatic generation of optimized C code with significant speedups;

Resilient - Ready to highly complex code restructuring and immune to non-included particular transformations.

Possible Applications

- High-Level Synthesis (HLS) hardware for FPGAs

-

Commercial Rights

INESC TEC has exclusive rights -

Development Stage

Lab Prototype (TRL 3-4) -

Further Information

Intellectual Property Status

Japan (granted)

USA (granted)

Europe (pending)

China (pending)

Opportunity

- Licensing (AGPLv3 or commercial license)

- Contract Research

Scientific Publications

Intelligent Information and Database Systems (2019), pp 230-244

-

Industrial Categories

Digital -

Tags

Graph transformations, FPGA, Hardware accelerators, High-Level synthesis (HLS)