Resumo

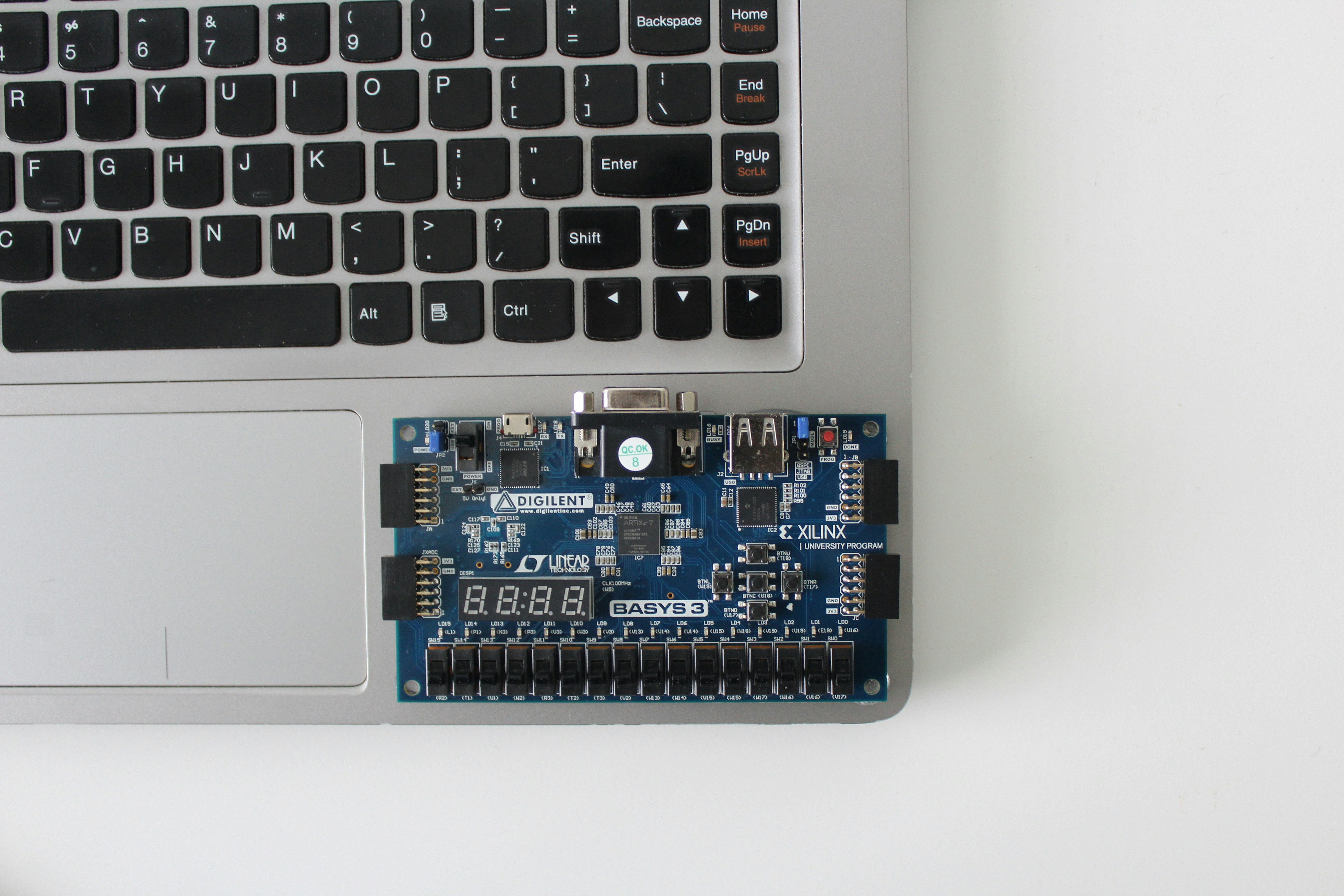

O CHARD é uma abordagem de reestruturação automática de código que reestrutura o código C como um diagrama de fluxo de dados (DFG), aplicando otimizações para gerar código C com diretivas para ferramentas de síntese de alto nível (HLS) - focadas em aceleradores de hardware baseados em FPGA.

A tecnologia permite aos programadores desenvolver FPGAs de forma fácil e eficiente, sem exigir um profundo conhecimento de design de hardware ou de ferramentas HLS, obtendo acelerações significativas e poupança de recursos - sobretudo quando comparadas com o código C original ou o código C otimizado manualmente, com diretivas HLS.

O CHARD visou alcançar:

- Uma aceleração até 81,7 vezes superior, com uma utilização de 0% de BRAM para kernels de sub-banda de filtro;

- Uma aceleração até 123 vezes superior, com uma utilização de 11% de BRAM para o kernel SVM;

- Uma aceleração até 76 vezes superior, com uma utilização de 0% de BRAM para o kernel de convolução 2D.

A tecnologia é implementada através de uma estrutura capaz de gerar código C automaticamente, compatível com HLS a partir de traços de execução das funções críticas de entrada. A estrutura também pode ser configurada pelos utilizadores, com vista a especificar o número de cargas/armazenamentos simultâneos, inputs e outputs e opções de otimização.

Desafio

Programar FPGA para a aceleração de hardware é uma tarefa complexa e demorada que requer competências e ferramentas específicas, diferentes do processo tradicional de programação de software.

Além disso, as ferramentas HLS existentes que permitem a utilização de linguagens semelhantes a C na programação de FPGA exigem experiência em hardware e transformações e diretivas manuais de código para gerar implementações de hardware eficientes. Estas limitações afetam a produtividade, o desempenho e a eficiência energética dos sistemas baseados em FPGA, especialmente para aplicações que envolvam cálculos paralelos e uso intensivo de dados, e.g., processamento de imagens, machine learning e algoritmos DSP.

Tecnologia

O CHARD efetua uma reestruturação automática, transformando o código C em DGF e aplicando otimizações para gerar código C com diretivas para HLS - focadas em aceleradores de hardware baseados em FPGA. A tecnologia permite aos programadores desenvolver FPGA de forma fácil e eficiente, sem exigir um profundo conhecimento de design de hardware ou de ferramentas HLS.

A tecnologia contribui com acelerações significativas e poupança de recursos - sobretudo quando comparada com o código C original ou o código C otimizado manualmente, com diretivas HLS:

- aceleração até 81,7 vezes superior para kernels de sub-banda de filtro (em comparação com código C original);

- aceleração até 5,8 vezes superior para kernels de sub-banda de filtro (em comparação com código C otimizado manualmente);

- aceleração até 123 vezes superior para o kernel SVM (em comparação com o código C original);

- aceleração até 3,5 vezes superior para o kernel SVM (em comparação com o código C otimizado manualmente);

- aceleração até 76 vezes superior para o kernel de convolução 2D (em comparação com o código C original);

- aceleração até 3 vezes superior para o kernel de convolução 2D (em comparação com o código C otimizado manualmente)

A tecnologia é baseada num frontend flexível capaz de lidar com diferentes linguagens de entrada, e um backend que implementa várias transformações e otimizações de diagramas, e.g., folding, unfolding, pipelining, otimizações aritméticas, particionamento de matrizes e reutilização de dados.

A tecnologia é implementada através de uma estrutura capaz de gerar código C automaticamente, compatível com HLS a partir de traços de execução das funções críticas de entrada. A estrutura também pode ser configurada pelos utilizadores, com vista a especificar o número de cargas/armazenamentos simultâneos, inputs e outputs e opções de otimização.

Principais Vantagens

O CHARD oferece vários benefícios e vantagens na otimização de algoritmos de processamento digital de sinais (DSP) em FPGA. Ao empregar diferentes técnicas de otimização, incluindo folding e unfolding de loop, pipelining, reutilização de dados e particionamento de matrizes, o CHARD garante a implementação eficiente de FPGA. Aqui estão algumas das principais vantagens desta tecnologia:

- Aceleração eficiente de hardware:o CHARD otimiza automaticamente o código C para uma aceleração eficiente de hardware, com ferramentas de síntese de alto nível (HLS) como backend. Este processo de otimização não requer especialistas em HLS, permitindo aos programadores alcançar essa mesma aceleração de hardware sem conhecimento especializado;

- Melhor desempenho:o código otimizado gerado pelo CHARD melhora significativamente o desempenho de aceleradores de hardware. Ao alavancar todo o potencial de FPGA, o CHARD permite um melhor desempenho e uma execução mais rápida dos algoritmos DSP;

- Flexibilidade em termos de linguagem:o CHARD permite a produção de DFG a partir de várias linguagens. Assim, os programadores que trabalham com diferentes linguagens de programação podem utilizar ferramentas HLS baseadas em C, garantindo mais flexibilidade e acessibilidade.

- Aumento da produtividade:o CHARD aumenta a produtividade ao simplificar o processo de design. Em comparação à programação manual de design RTL (Register Transfer Level), o CHARD garante mais poder, maior desempenho e PPA superiores, em menos tempo. Assim, os programadores obtêm resultados otimizados sem investir grande esforço manual;

- Uso simplificado de ferramentas:os programadores de software podem utilizar ferramentas HLS, mesmo que não tenham experiência em hardware ou transformações manuais de código. O CHARD apoia o trabalho dos programadores ao automatizar o processo de otimização e ao facilitar o recurso a aceleração baseada em FPGA;

- Compatibilidade com múltiplas linguagens: O CHARD suporta várias linguagens de entrada e modelos de programação através de um código de instrumentação adequado. Esta compatibilidade permite aos programadores tirar o máximo partido desta tecnologia, independentemente da linguagem de programação que utilizam;

- Aceleração significativa e redução em termos de recursos:o CHARD permite acelerações elevadas e a redução de recursos em diversas aplicações de benchmark. Certos algoritmos e.g., filtro de sub-banda, autocorrelação, 1D FIR (Finite Impulse Response), convolução 2D e SVM (Support Vetor Machine) obtêm melhorias em termos de desempenho, sendo a utilização de recursos mais eficiente graças ao CHARD;

- Otimização automatizada comparável às abordagens manuais:o CHARD gera automaticamente um código semelhante e, em alguns casos, superior ao código otimizado manualmente com diretivas. Este recurso economiza tempo e reduz o nível de esforço, garantindo resultados otimizados.

Possíveis Aplicações e Casos de Uso

O CHARD é uma tecnologia que permite a reestruturação automática de código na utilização de HLS para aceleradores de hardware baseados em FPGA. Esta tecnologia pode ser útil em várias aplicações que exigem aceleração eficiente de hardware, com recurso a FPGA e HLS.

- Algoritmos de processamento digital de sinais (DSP):o CHARD consegue otimizar algoritmos DSP para a implementação de FPGA, garantindo acelerações significativas e melhorias na utilização de recursos;

- Computação de alto desempenho (HPC):o CHARD pode gerar implementações eficientes de hardware em aplicações HPC, muitas vezes apenas possíveis com a utilização de técnicas de reestruturação manual do código do software de entrada e da inserção manual de diretivas HLS adequadas;

- Machine earning:o CHARD garante a otimização de algoritmos de machine learning para a implementação de FPGA, facilitando o desenvolvimento de aceleradores de hardware mais rápidos e eficientes;

- Processamento de vídeo e de áudio:o CHARD é capaz de otimizar algoritmos de processamento de vídeo e de áudio para a implementação de FPGA, facilitando o desenvolvimento de aceleradores de hardware mais rápidos e eficientes;

- Qualquer aplicação que exija a aceleração de hardware com recurso a ferramentas FPGAs e HLS.

-

Direitos Comerciais

Exclusivo -

Estado de desenvolvimento

Lab Prototype (TRL 3-4) -

Outras informações

Patente

Publicações

-

Disponibilidade de licenciamento

Mundial -

Categorias industriais

Digital -

Tags

Reestruturação de diagramas, Arranjo de portas programáveis em campo, Aceleradores de hardware, Ferramenta de síntese de alto nível